| Status | Available |

| Access arrangements | Contact Dr Owain Kenway |

| Organisations | University College London, STFC, Graphcore |

| Project linkage | Various |

This testbed evaluated the Graphcore IPU-M2000 system for high performance and scientific computing applications, providing a novel architecture for the community to test and develop AI compatible codes on. The IPU (Intelligent Processing Unit) is a completely new kind of massively parallel processor, co-designed from the ground up to accelerate machine intelligence.

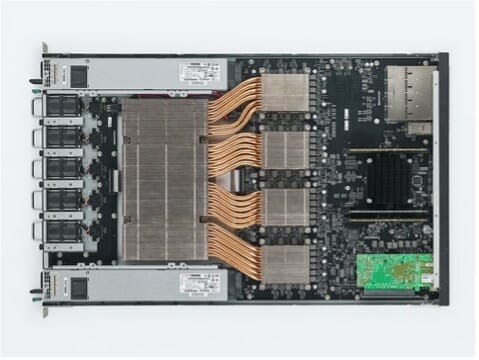

Each MK2 GC200 IPU in the IPU-M2000 unit has 1,472 processor cores, running nearly 9,000 independent parallel program threads with 900MB in processor memory and 250 TeraFlops of AI compute at FP16.16 and FP16.SR (stochastic rounding). The IPU-M2000 system has four IPUs, delivering approximately 1 PetaFlop of AI compute, and supporting ultra-low latency IPU-Fabric interconnect.

The testbed includes four IPU-M2000 systems, enabling the interconnect to be tested and characterised. The project has evaluated the Graphcore system’s intended use cases around AI training and interference, and also looked at a subset of HPC codes that may be suitable for this platform. The Graphcore system is also available to the ExCALIBUR and wider UK research community with support and a training programme from the UCL team. It should be noted that codes will need to fit into small memories and must be single or half precision due to IPU requirements.